Yarı iletken sektörünün devlerinden TSMC, yapay zeka yongalarına yönelik artan talebi karşılamak amacıyla yonga (çip) paketlemede devrim niteliğinde bir yöntemi hayata geçirmeye hazırlanıyor. Nikkei Asia’nın özel haberine göre, sektörde “panel düzeyinde” (panel-level) olarak adlandırılan gelişmiş çip paketleme teknolojisi için teknik standartları belirlemede sona yaklaşıldı. Küçük hacimli üretimin 2027 yılı itibarıyla başlaması hedefleniyor.

Yarı iletken sektörünün devlerinden TSMC, yapay zeka yongalarına yönelik artan talebi karşılamak amacıyla yonga (çip) paketlemede devrim niteliğinde bir yöntemi hayata geçirmeye hazırlanıyor. Nikkei Asia’nın özel haberine göre, sektörde “panel düzeyinde” (panel-level) olarak adlandırılan gelişmiş çip paketleme teknolojisi için teknik standartları belirlemede sona yaklaşıldı. Küçük hacimli üretimin 2027 yılı itibarıyla başlaması hedefleniyor. Yuvarlaktan kareye geçiş

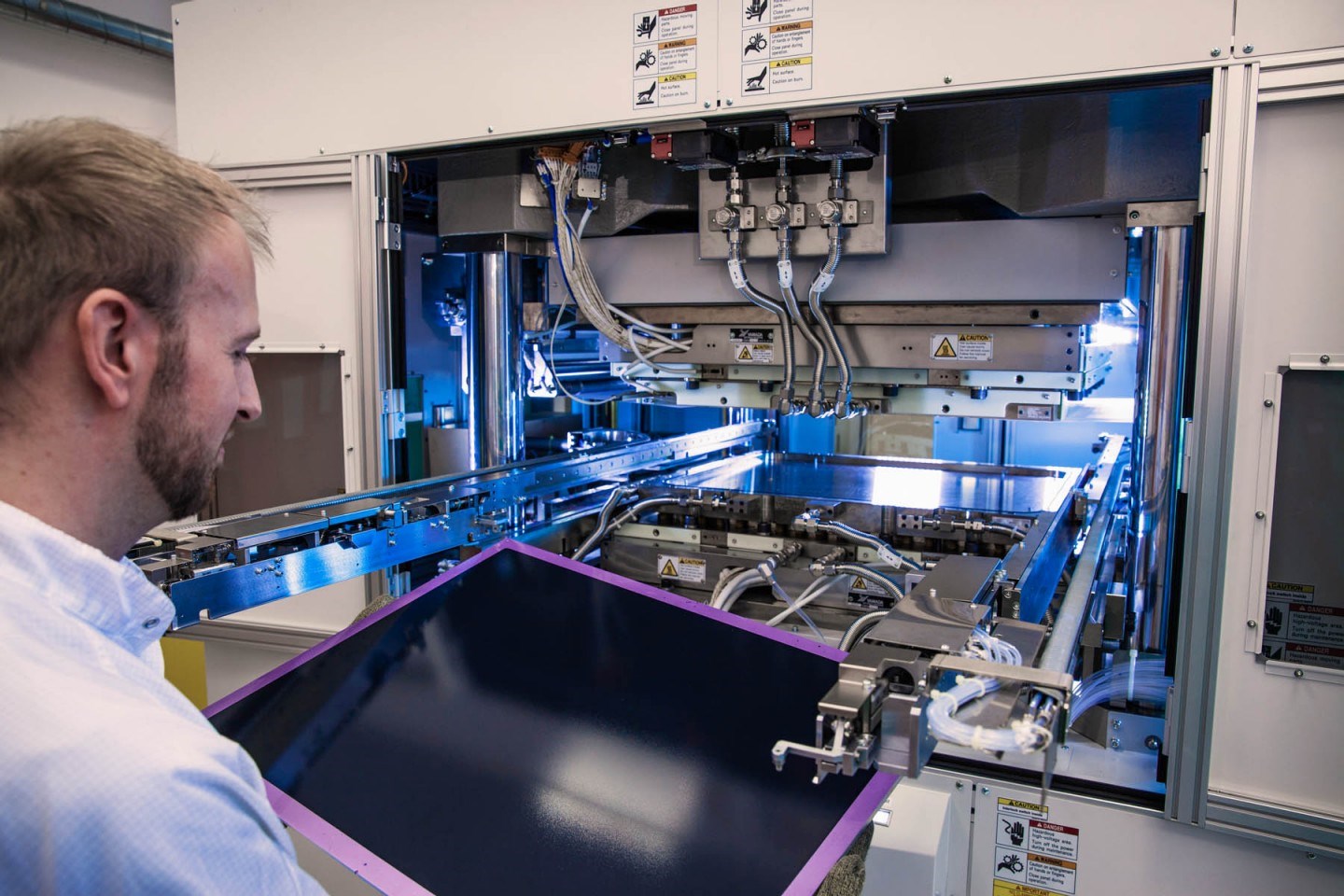

Geleneksel yonga üretimi genellikle 300 milimetrelik yuvarlak yonga plakaları (wafer) üzerinde gerçekleştirilirken, TSMC’nin yeni yöntemi kare formdaki alt tabakaları (substrate) esas alacak. İlk nesil üretim için düşünülen boyut 310 mm x 310 mm olacak. Bu ölçü, şirketin daha önce test ettiği 510 mm x 515 mm’lik daha büyük panellere kıyasla mütevazı kalsa da, klasik yuvarlak plakalara göre daha fazla yarı iletkeni barındırabilecek.

TSMC’ye yakın kaynaklar, bu tercihin bilinçli bir şekilde kalite kontrolünü sıkı tutmak amacıyla yapıldığını belirtiyor. Zira özellikle kimyasal kaplama sürecinin kare bir yüzeye eşit şekilde uygulanması, mühendislik açısından oldukça zorlu bir adım olarak öne çıkıyor.

TSMC’ye yakın kaynaklar, bu tercihin bilinçli bir şekilde kalite kontrolünü sıkı tutmak amacıyla yapıldığını belirtiyor. Zira özellikle kimyasal kaplama sürecinin kare bir yüzeye eşit şekilde uygulanması, mühendislik açısından oldukça zorlu bir adım olarak öne çıkıyor. Yeni üretim tekniği yalnızca TSMC’nin değil, küresel yonga üretim ekosisteminin tamamını etkileyebilir. ABD, Japonya ve Tayvan’daki ekipman üreticileri, kare şekilli tabanlara uygun yeni üretim araçları tasarlamaya başladı bile. Robotik kollar gibi taşıma ekipmanlarının da yeni formata uyarlanması gerekiyor.

Aktarılanlara göre kare yapı, kenar boşluğunu azaltarak daha verimli bir alan kullanımı sağlayacak. TSMC, bu teknolojinin ticarileştirilmesi için Tayvan’ın Taoyuan kentinde bir pilot üretim hattı kuruyor. Hedef, 2027 civarında sınırlı da olsa üretime geçmek.

Çip paketleme artık çok önemli

Çip paketleme geçmişte çip üretimine göre daha düşük teknolojik bir işlem olarak görülüyordu. Ancak günümüzde, özellikle yapay zekaya özel çiplerde performansı belirleyen kritik bir unsur haline geldi. TSMC’nin halihazırda sunduğu CoWoS (Chip-on-Wafer-on-Substrate) teknolojisi, Nvidia’nın Blackwell Superchip’lerinden Broadcom, Amazon, Google ve AMD gibi devlerin çözümlerine kadar birçok gelişmiş sistemin temelinde yer alıyor.

YORUM